# **MITSUBISHI**

Digital-Analog Converter Module Type A616DAI

# User's Manual

# SAFETY PRECAUTIONS ●

(Always read these instructions before using this equipment.)

Before using this product, please read this manual and the relevant manuals introduced in this manual carefully and pay full attention to safety to handle the product correctly.

The instructions given in this manual are concerned with this product. Refer to the User's Manual of the CPU module in use for details on the safety instructions for the programmable logic controller system.

In this manual, the safety instructions are ranked as "DANGER" and "CAUTION".

Indicates that incorredt handling may cause hazardous conditions, resulting in death or severe injury.

Indicates that incorredt handling may cause hazardous conditions, resulting in medium or slight personal injury or physical damage.

Note that the **CAUTION** level may lead to a serious consequence according to the circumstances. Always follow the instructions of both levels because they are important to personal safety.

Please save this manual to make it accessible when required and always forward it to the end user.

# [DESIGN PRECAUTIONS]

# **!** DANGER

- Install a safety circuit external to the PLC that keeps the entire system safe even when there

are problems with the external power supply or the PLC module.

Otherwise, trouble could result from erroneous output or erroneous operation.

- (1) The analog output state will differ according to the setting state of the various functions for controlling the analog output.

Take special care when making the settings.

Refer to section 3.3 for details on the analog output state.

- (2) If there is a fault in the output element or the internal circuit, correct outputs may not be possible or erroneous outputs may be made. Provide a circuit to externally monitor output signals that could lead to major faults.

- When DC±15V power is supplied exterhally, make so that this is a system that will simultaneously be turned on and off with the A616DA system. If the power for the A616DA system is turned on/off while external power is being supplied the erroneous output could cause an accident.

# **ACAUTION**

- Do not bunch the control wires or communication cables with the main circuit or power wires, or install them close to each other.

- They should be installed 100mm (3.94inch) or more from each other. Not doing so could result in noise that would cause erroneous operation.

- At power ON/OFF, voltage or current may instantaneously be output from the output terminal of this module. In such case, wait until the analog output becomes stable to start controlling the external device.

### [INSTALLATION PRECAUTIONS]

# **ACAUTION**

- Use the PLC in an environment that meets the general specifications given in the User's Manual of the CPU module in use.

- Using this PLC in an environment outside the range of the general specifications could result in electric shock, fire, erroneous operation, and damage to or deterioration of the product.

- Securely insert the module fixing latch on the module bottom into the fixing holes on the base unit before mounting. Incorrect mounting of the module could lead to erroneous operation, faults or drop.

For use in the environment of frequent vibration, tighten the module with screws.

- Do not directly touch the module's conductive parts or electronic components.

Touching the conductive parts could cause an operation failure or give damage to the module.

- Tighten the terminal screws with the specified torque.

If the terminal screws are loose, it could result in short circuits, five or erroneous operation.

Overtightening can cause a drop, short circuits or malfunction due to damage to the screw or module.

### [WIRING PRECAUTIONS]

# **ACAUTION**

- Always ground the FG terminal for the PLC.

There is a risk of malfunction.

- When wiring in the PLC, be sure that it is done correctly by checking the product's rated voltage and the terminal layout.

Connecting a power supply that is different form the rating or incorrectly wiring the product could result in fire or damage.

- Tighten the terminal screws with the specified torque.

If the terminal screws are loose, it could result in short circuits, fire, or erroneous operation.

Overtightening can cause a drop, short circuits or malfunction due to damage to the screw or module.

- Be sure there are no foreign substances such as sawdust or wiring debris inside the module. Such debris could cause fires, damage, or erroneous operation.

### [STARTUP AND MAINTENANCE PRECAUTIONS]

# **CAUTION**

- Do not disassemble or modify the module.

Doing so could cause trouble, erroneous operation, injury, or fire.

- Switch all phases of the external power supply off before mounting or removing the module.

If you do not switch off the external power supply, it will cause failure or malfunction of the module.

- Do not touching the terminals with power on. Failure to observe this could lead to erroneous operation.

- Before loading or unloading the communication board, communication module or memory board to or from the GOT, always switch off the GOT power externally in all phases.

Not doing so can cause a module failure or malfunction.

If the terminal screws are loose, it could result in short circuits, five or erroneous operation. Overtightening can cause a drop, short circuits or malfunction due to damage to the screw or module.

- Do not disassemble or modify the module.

Doing so could cause trouble, erroneous operation, injury, or fire.

- Switch all phases of the external power supply off before mounting or removing the module.

If you do not switch off the external power supply, it will cause failure or malfunction of the module.

- Before handling the module, always touch grounded metal, etc. to discharge static electricity from the human body.

Failure to do so can cause the module to fail or malfunction.

### [DISPOSAL PRECAUTIONS]

# **ACAUTION**

• When disposing of the product, handle it as industrial waste.

### **REVISIONS**

\*The manual number is given on the bottom left of the back cover.

| Print Date | *Manual Number  | Revision                                                                                                                                                                      |

|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mar., 1989 | IB (NA) 66173-A | First edition                                                                                                                                                                 |

| Apr., 2001 | IB (NA) 66173-B | Addition  SAFETY PRECAUTIONS, WARRANTY  Correction  Section 1.2, 2.1.1, 2.2, 2.3, 3.1, 3.2, 3.3, 3.4.2, 4.2, 4.6.2, 5.2.1, 5.4.1, 5.4.3, 6.4, Appendix 2.1, 3.1, 3.2.1, 3.2.2 |

| Nov., 2004 | IB (NA) 66173-C | Addition Chapter 5 Correction SAFETY PRECAUTIONS, Section 3.1, 4.2, 5.3.5, WARRANTY                                                                                           |

|            |                 |                                                                                                                                                                               |

|            |                 |                                                                                                                                                                               |

|            |                 |                                                                                                                                                                               |

|            |                 |                                                                                                                                                                               |

|            |                 |                                                                                                                                                                               |

|            |                 |                                                                                                                                                                               |

| i          |                 |                                                                                                                                                                               |

# **MEMO**

### INTRODUCTION

Thank you for choosing the Mitsubishi MELSEC-A Series of General Purpose Programmable Controllers. Please read this manual carefully so that the equipment is used to its optimum. A copy of this manual should be forwarded to the end User.

| 1. INTRODUCTION                          |  |

|------------------------------------------|--|

| 2. SYSTEM CONFIGURATION                  |  |

| 3. SPECIFICATIONS                        |  |

| 4. PRE-OPERATION SETTINGS AND PROCEDURES |  |

| 5. PROGRAMMING                           |  |

| 6. TROUBLESHOOTING                       |  |

| APPENDICES                               |  |

# **CONTENTS**

| 1.  | INTRODUCTION1                                                                 | -1 <b>~</b> 1-2 |

|-----|-------------------------------------------------------------------------------|-----------------|

| 1.1 |                                                                               |                 |

| 1.2 | Generic Names of CPUs ·····                                                   | 1-2             |

| 2.  | SYSTEM CONFIGURATION2                                                         | -1 ~ 2-4        |

| 2.1 | Overall Configuration ······                                                  | 2-1             |

|     | 2.1.1 Building block type CPU system ······                                   | 2-1             |

|     | 2.1.2 Compact type CPU system······                                           | 2-2             |

| 2.2 | Applicable A-Series Systems ······                                            | 2-3             |

| 2.3 |                                                                               | 2-4             |

| 3.  | SPECIFICATIONS 3-                                                             | 1 ~ 3-10        |

| 3.1 | General Specifications ······                                                 | 3-1             |

| 3.2 |                                                                               | 3-2             |

| 3.3 |                                                                               | 3-4             |

| 3.4 |                                                                               | 3-5             |

|     | 3.4.1 I/O conversion characteristics······                                    |                 |

|     | 3.4.2 I/O conversion characteristics in response to offset/gain value changes | 3-7             |

| 3.5 | D/A Conversion Processing Time·····                                           | 3-8             |

|     | 3.5.1 Sampling period                                                         | 3-8             |

|     | 3.5.2 Conversion speed······                                                  | 3-8             |

| 3.6 |                                                                               | 3-9             |

| 3.7 | External Supply Power (±15V DC) Specifications                                | 3-10            |

| 4.  | PRE-OPERATION SETTINGS AND PROCEDURES 4-                                      |                 |

| 4.1 | Pre-Operation Procedure                                                       | 4-1             |

| 4.2 | Handling Instructions ······                                                  | 4-2             |

| 4.3 | Nomenclature ·····                                                            | 4-3             |

| 4.4 | Settings·····                                                                 | 4-5             |

|     | 4.4.1 Setting analog output to HOLD/CLEAR ······                              | 4-5             |

| 4.5 | Offset/Gain Setting                                                           |                 |

|     | 4.5.1 Notes on offset/gain setting ······                                     | 4-6             |

|     | 4.5.2 Offset/gain setting procedure ······                                    | 4-8             |

| 4.6 | Wiring ·····                                                                  |                 |

|     | 4.6.1 Wiring instructions ·····                                               | 4-9             |

|     | 4.6.2 Connection of A616DA and external devices······                         | 4-9             |

|     | 4.6.3 Connection of ±15V DC to the A616DA······                               | ····· 4-10      |

| 5. F            | PROGRAM  | MMING     | ••••••                          |                                                                        | ····· 5-1 ~ 5-16 |

|-----------------|----------|-----------|---------------------------------|------------------------------------------------------------------------|------------------|

| 5.1             | Progran  | nmina     | Procedure                       |                                                                        | 5-1              |

| 5.2             | I/O List | for ACI   | U                               |                                                                        | 5-2              |

|                 | 5.2.1 l  | nput lis  | t · · · · · · · · · · · · · · · |                                                                        | 5-2              |

|                 | 5.2.2    | Output    | ist                             |                                                                        | 5-3              |

| 5.3             | Ruffer N | Memor     | ,                               |                                                                        | 5-4              |

|                 | 5.3.1    | Buffer r  | nemorv as                       | signment ·····                                                         | 5-4              |

|                 | 5.3.2    | D/A cor   | version en                      | nable/disable channel area (Address 0 <sub>H</sub> ) ······            | 5-5              |

|                 | 5.3.3    | Analog    | output ena                      | able/disable channel area (Address 14) ······                          | 5-5              |

|                 | 5.3.4    | CH.0 to   | CH.F digita                     | al value area (Addresses 10 <sub>H</sub> to 1F <sub>H</sub> )······    | ····· 5-6        |

|                 | 5.3.5    | CH.0 to   | CH.F set va                     | alue check code area (Addresses 30+ to 3F+) ······                     | 5-6              |

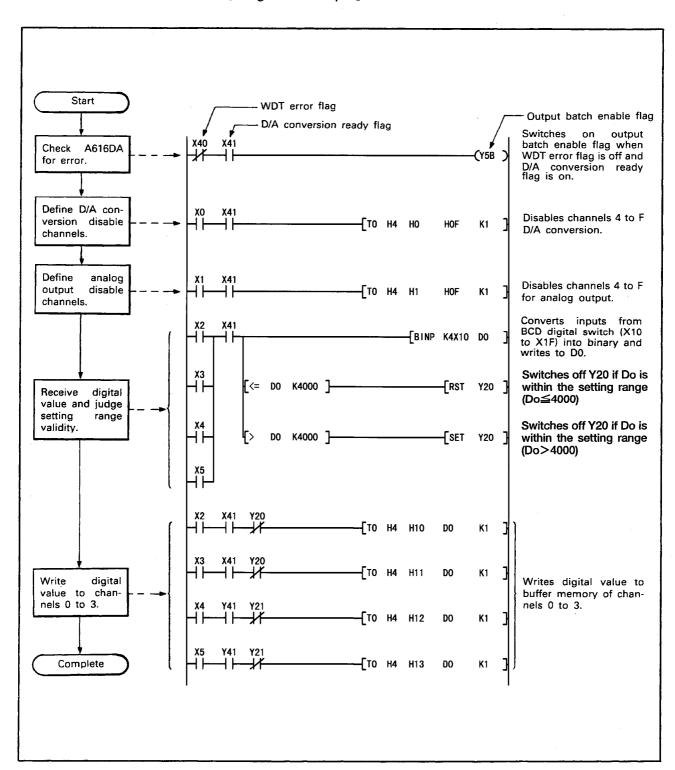

| 5.4             | Program  | m Exan    | ples for Br                     | uilding Block Type CPU······                                           | 5-7              |

|                 | 5.4.1    | Digital ' | alue settir                     | ng program ······                                                      | 5-7              |

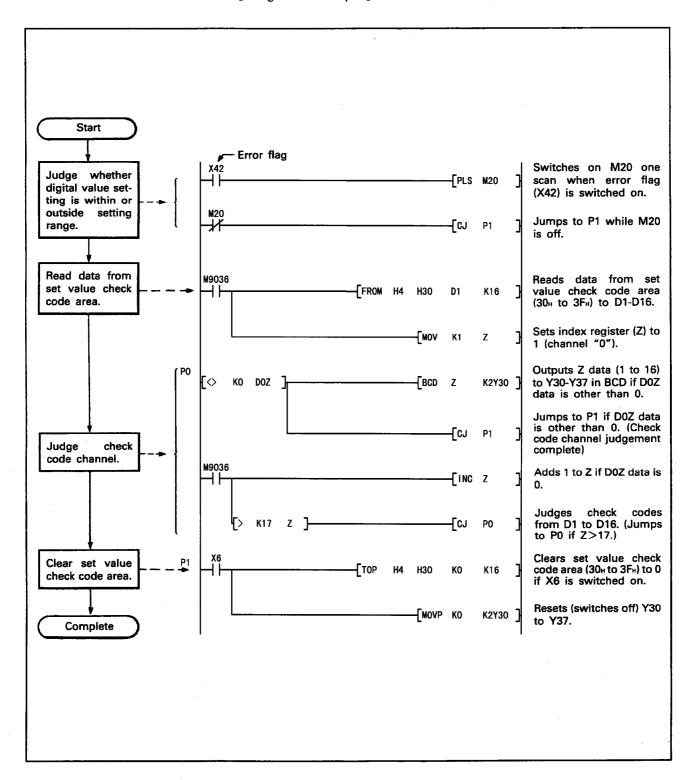

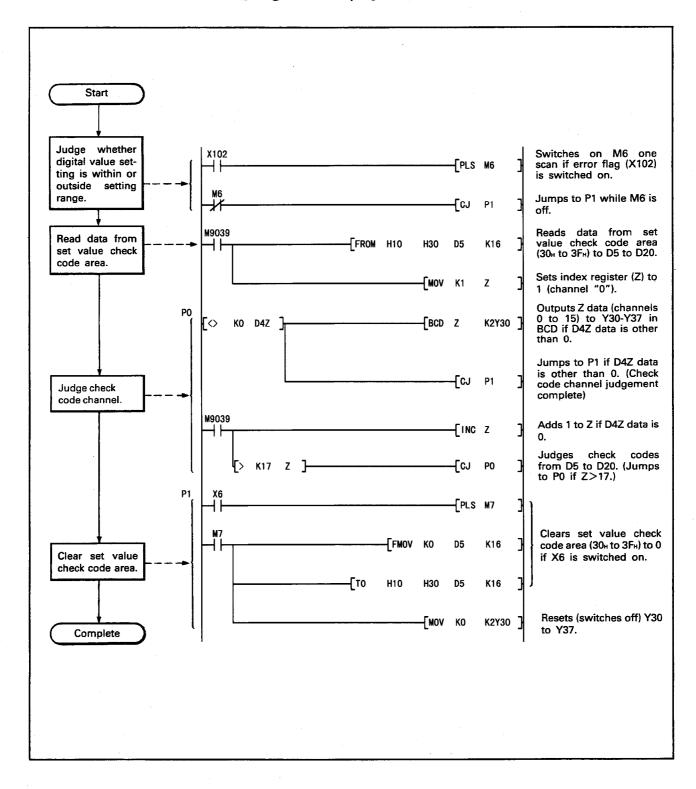

|                 | 5.4.2 I  | Digital ' | alue settir                     | ng error detection program·····                                        | 5-9              |

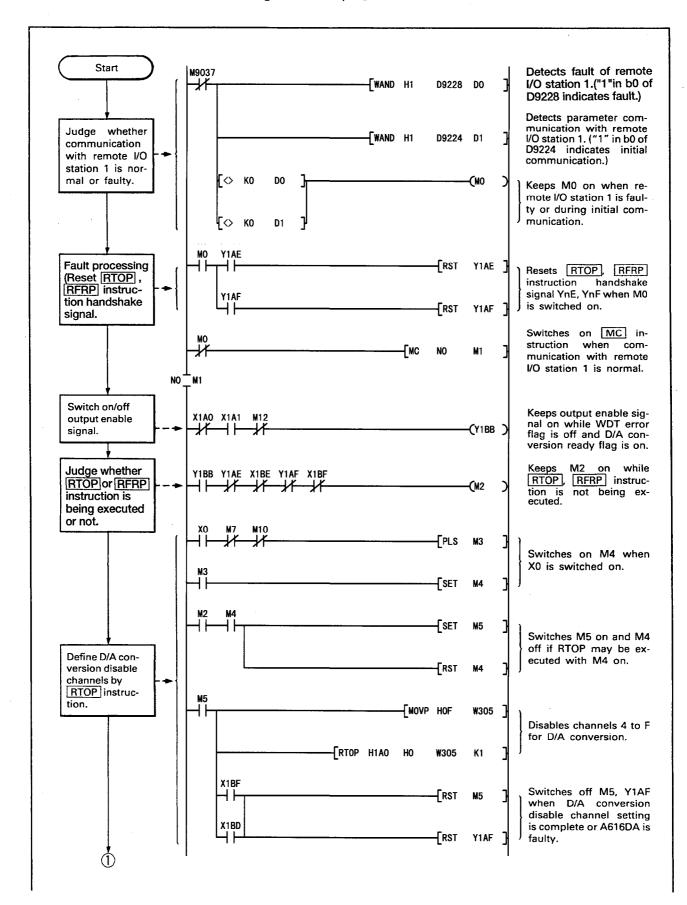

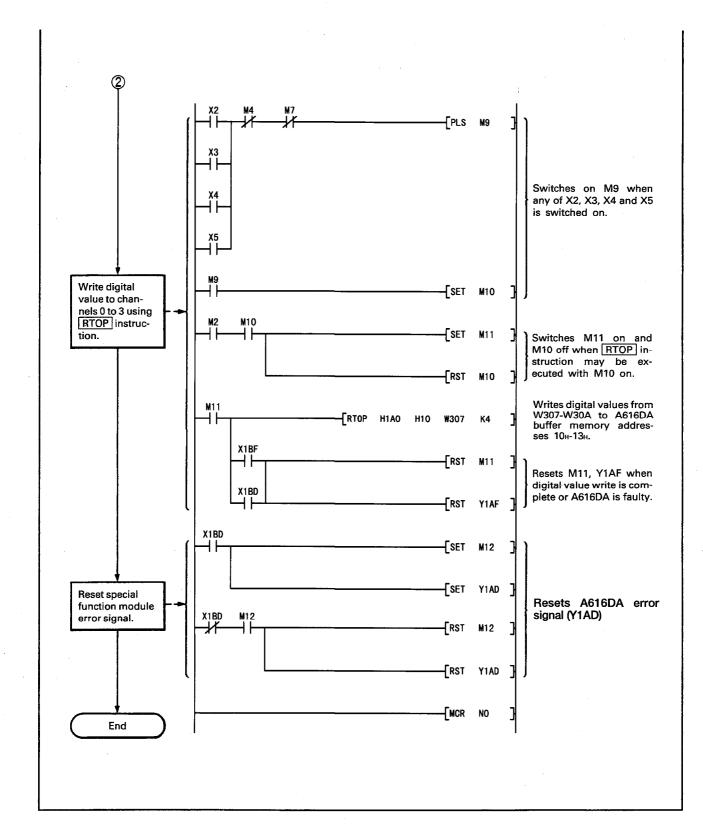

|                 | 5.4.3    | Prograi   | n for the A                     | 616DA loaded in remote I/O station ·····                               | 5-11             |

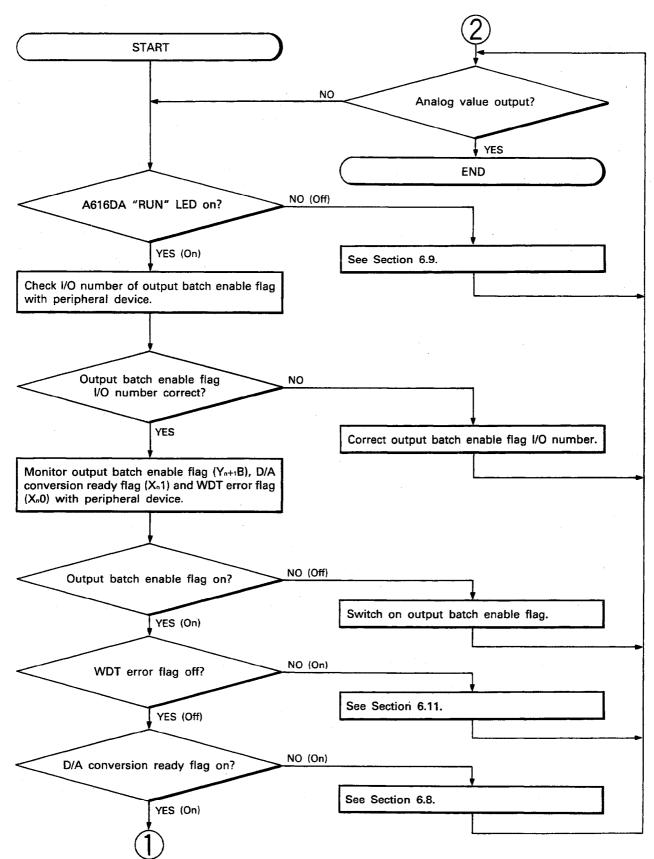

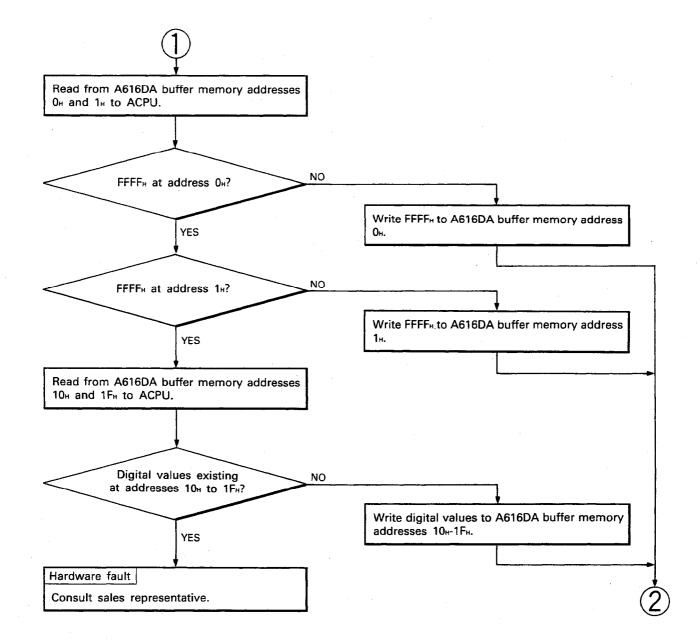

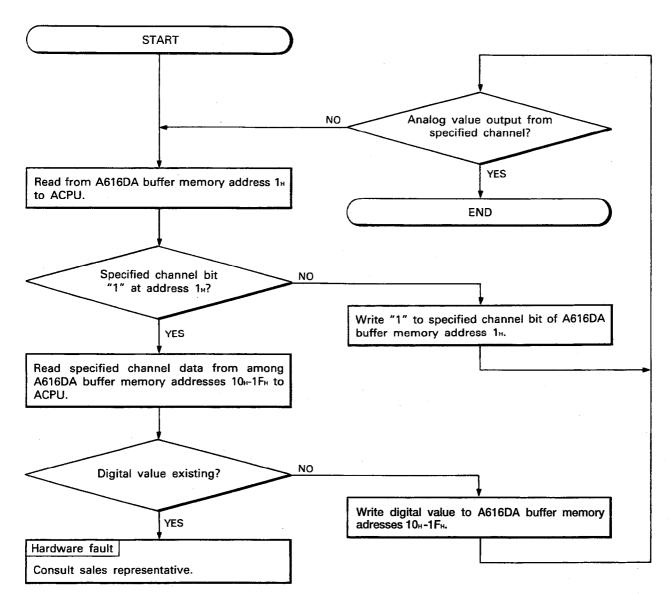

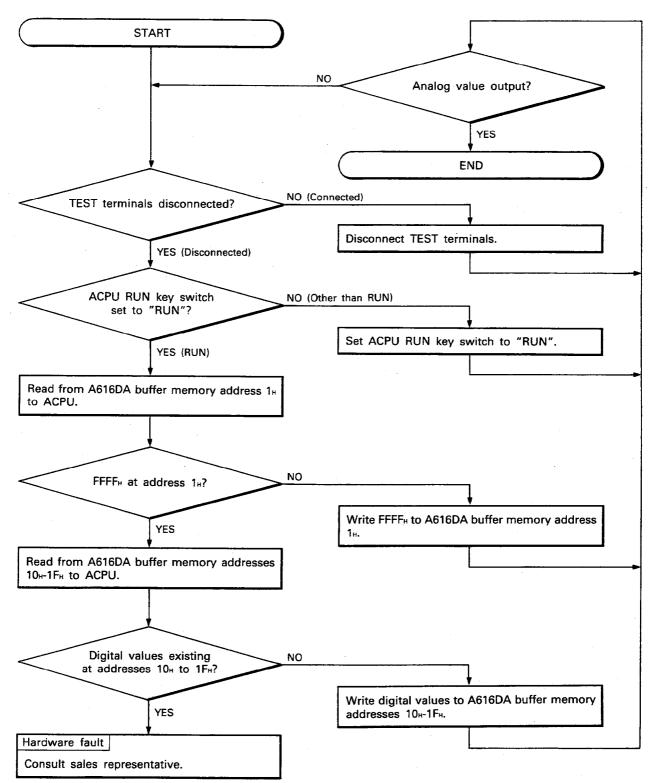

| 6. <sup>-</sup> | TROUBLE  | SHOO      | ING ······                      |                                                                        | ····· 6-1 ~ 6-19 |

|                 |          |           |                                 |                                                                        |                  |

| 6.1             | Sympto   | oms ····  |                                 |                                                                        | 6-1              |

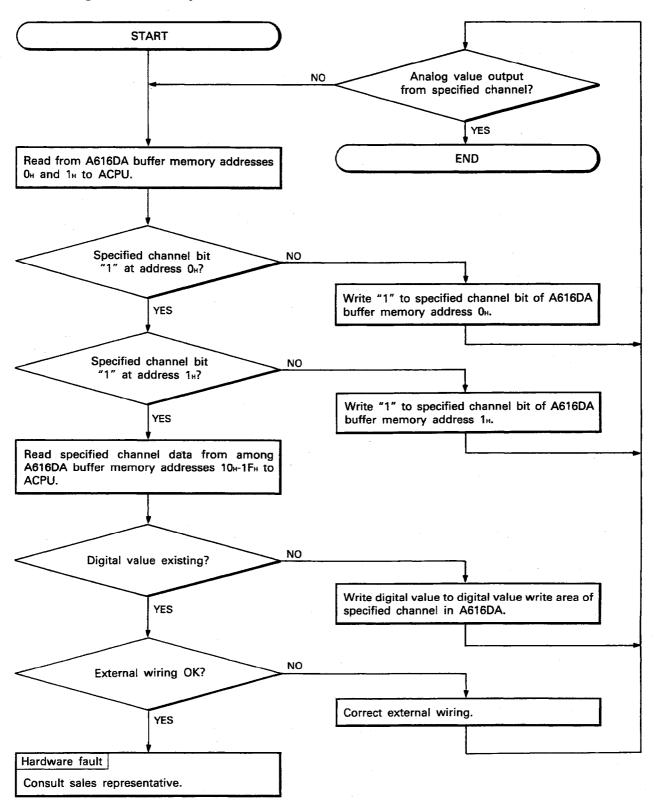

| 6.2             | Analog   | Value     | of Only Giv                     | ven Channel is 0mA ······                                              | 6-2              |

| 6.3             | Analog   | Values    | of All Cha                      | nnels are 0mA                                                          | 6-3              |

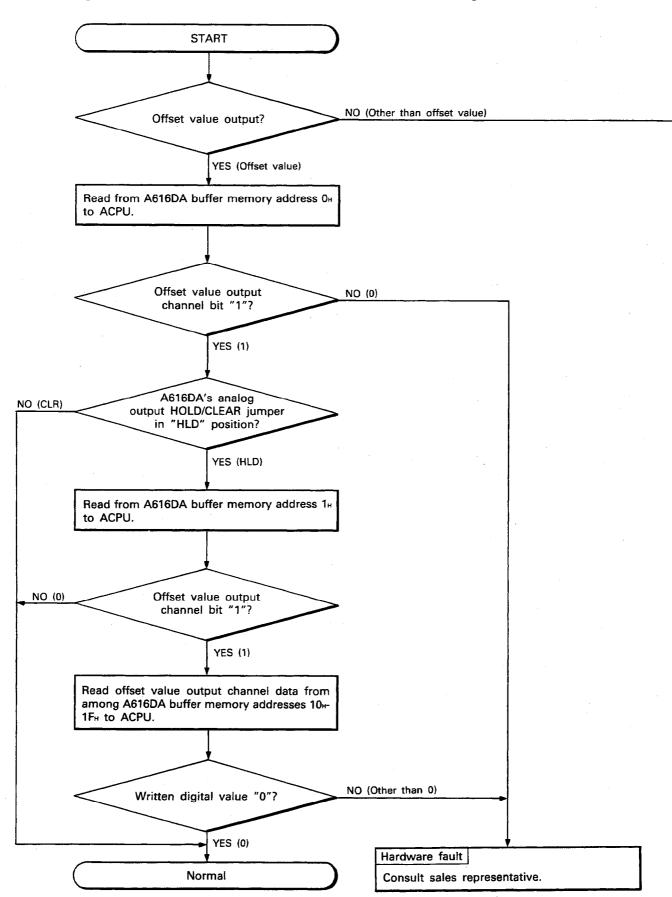

| 6.4             | Analog   | Value     | of Only Giv                     | ven Channel is Offset Value······                                      | 6-5              |

| 6.5             | Analog   | Values    | of All Cha                      | nnels are Offset Values ······                                         | 6-6              |

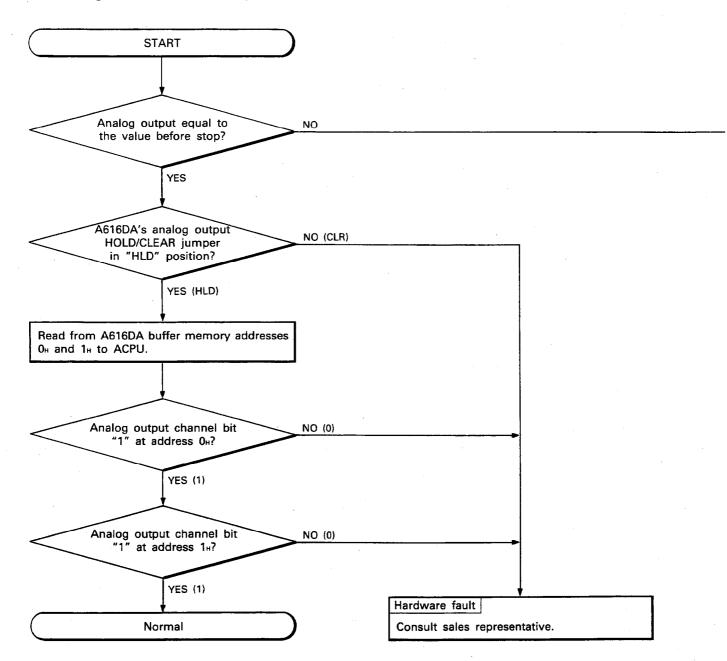

| 6.6             | Analog   | Value     | Remains O                       | Output at Stop of ACPU                                                 | 6-7              |

| 6.7             | Analog   | Value     | Remains O                       | Output with Output Batch Enable Flag ( $Y_{(n+1)}B$ ) Off $\cdot\cdot$ | 6-9              |

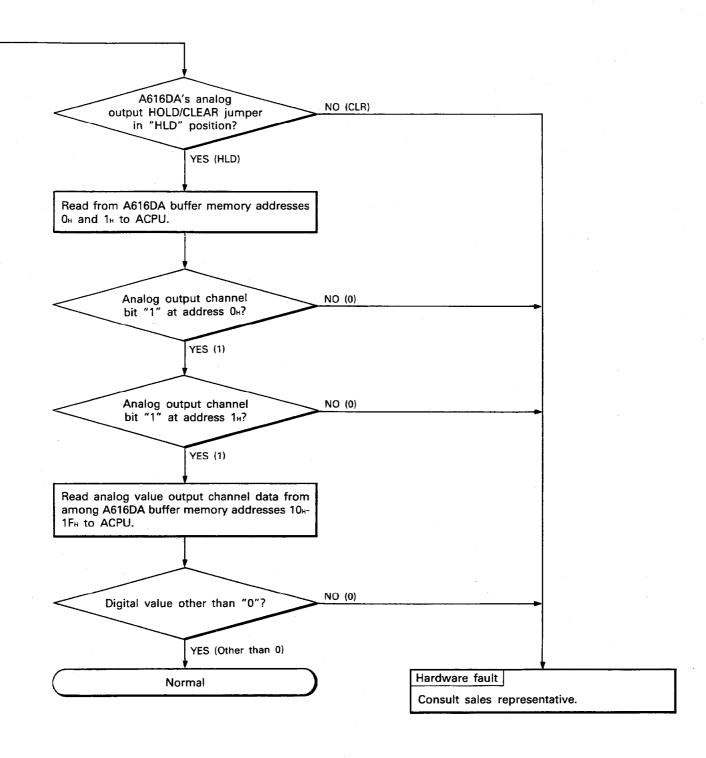

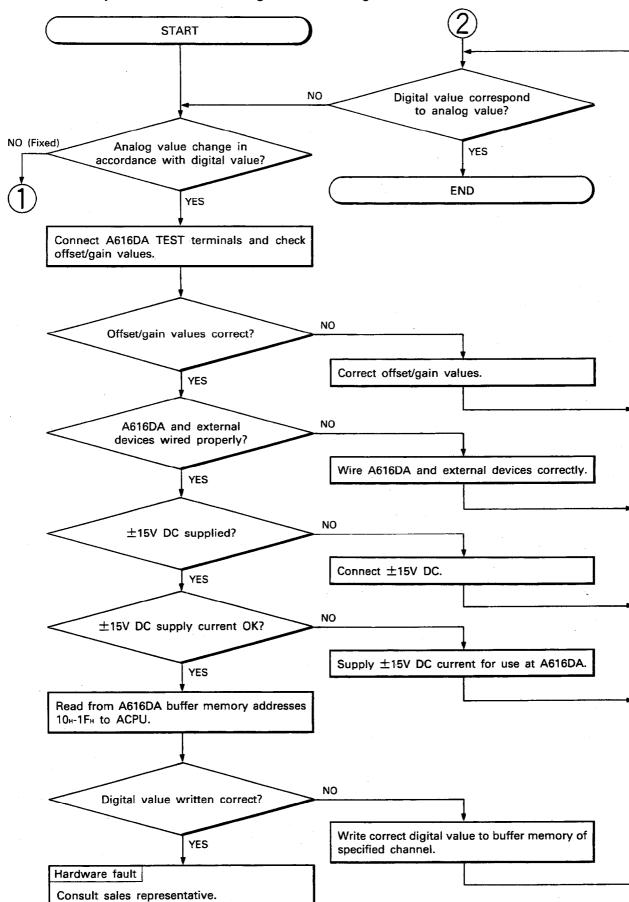

| 6.8             | No Cor   | respon    | dence betv                      | veen Digital and Analog Values······                                   | 6-11             |

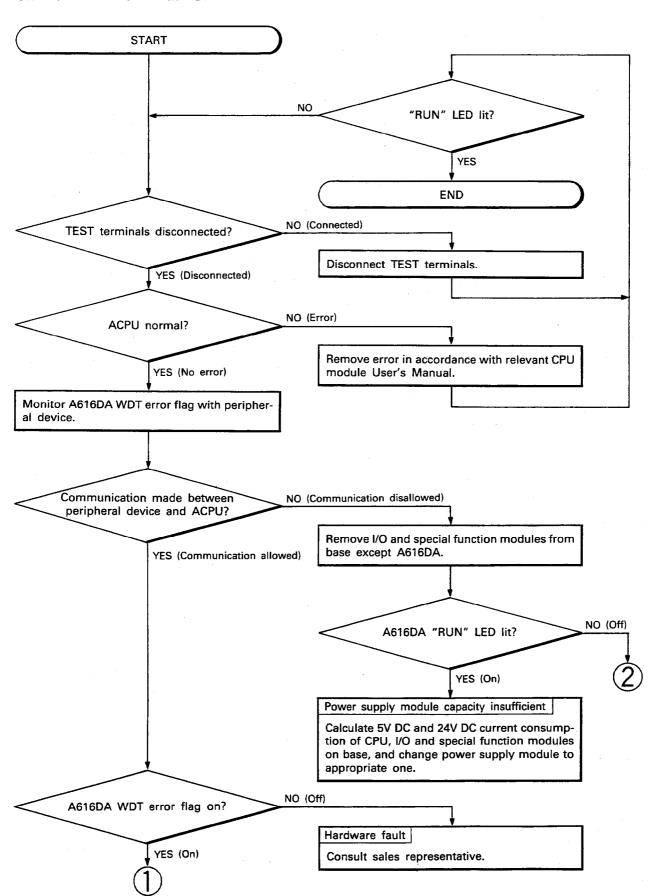

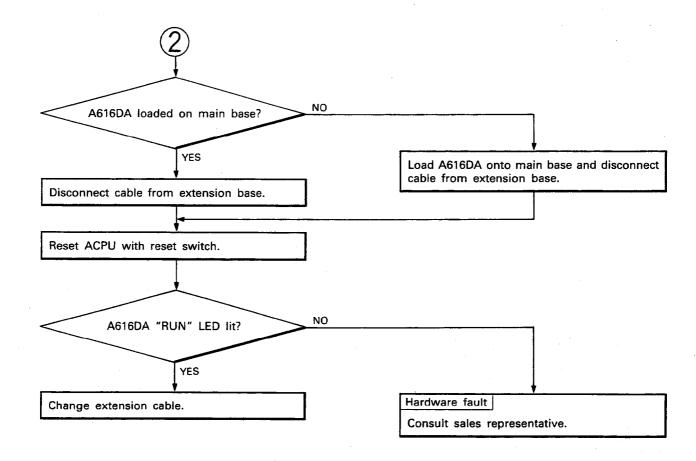

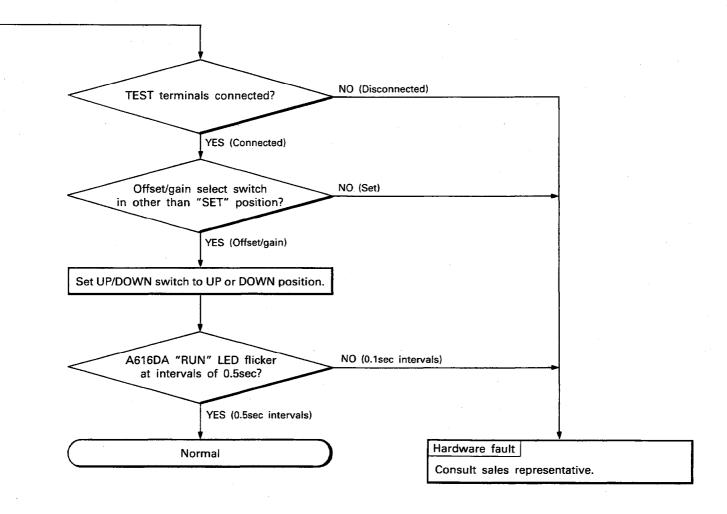

| 6.9             | A616D/   | A "RUN    | " LED Off                       |                                                                        | 6-13             |

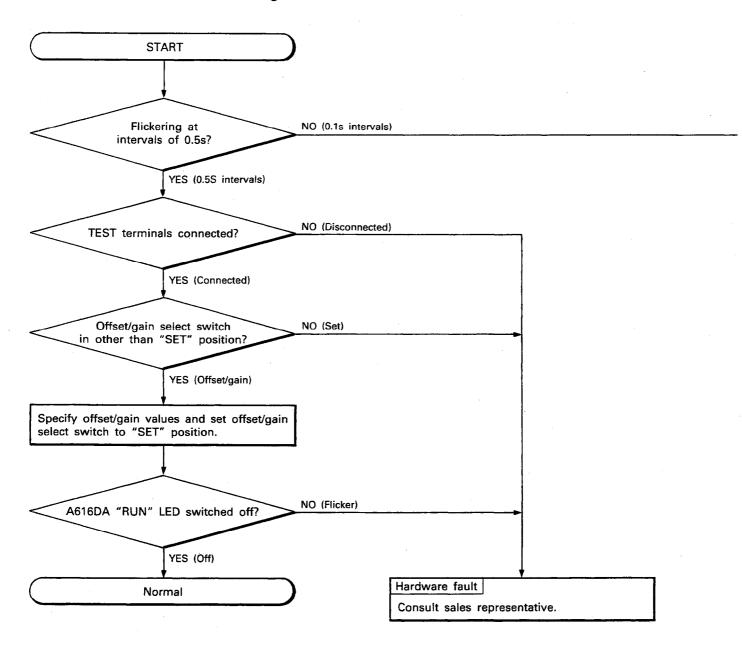

| 6.10            | A616D/   | A "RUN    | " LED Flic                      | kering·····                                                            | 6-15             |

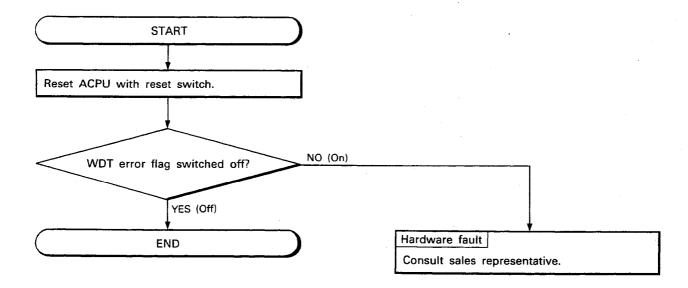

| 6.11            | A616D/   | A WDT     | Frror Flag                      | (X <sub>0</sub> 0) On ······                                           | 6-17             |

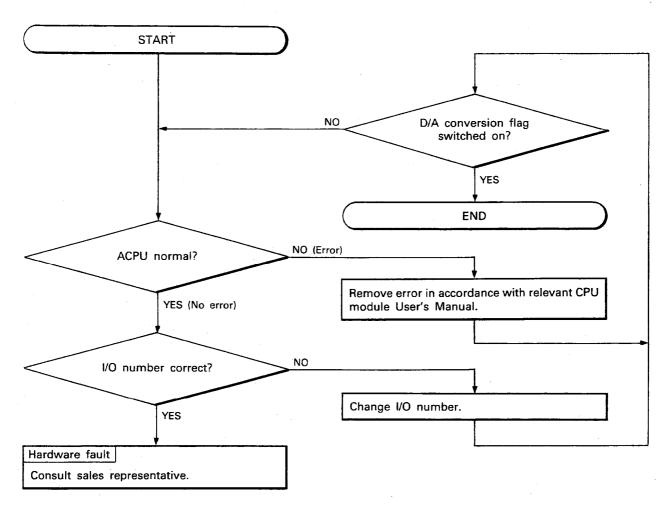

| 6.12            | D/A Co   | nversio   | n Ready Fl                      | ag (X₀1) Remains Off ·······                                           | 6-18             |

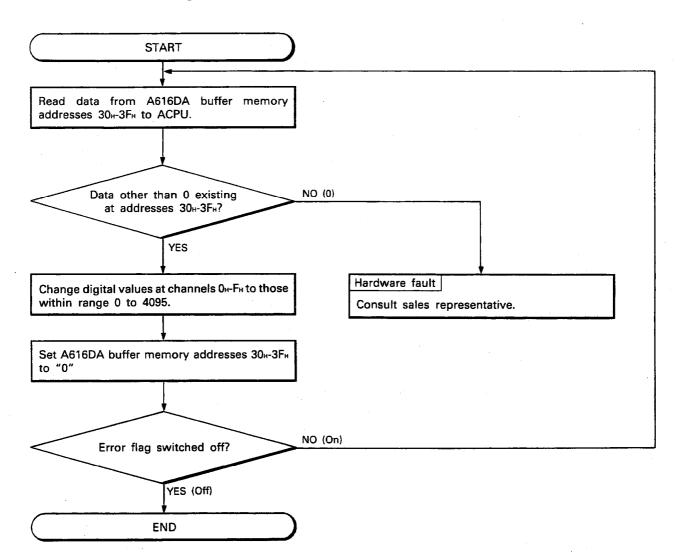

| 6.13            | A616D/   | A Error   | Flag (X <sub>n</sub> 2)         | On                                                                     | 6-19             |

| APP             | ENDICES  | <b>;</b>  | •••••                           |                                                                        | \PP-1 ~ APP-10   |

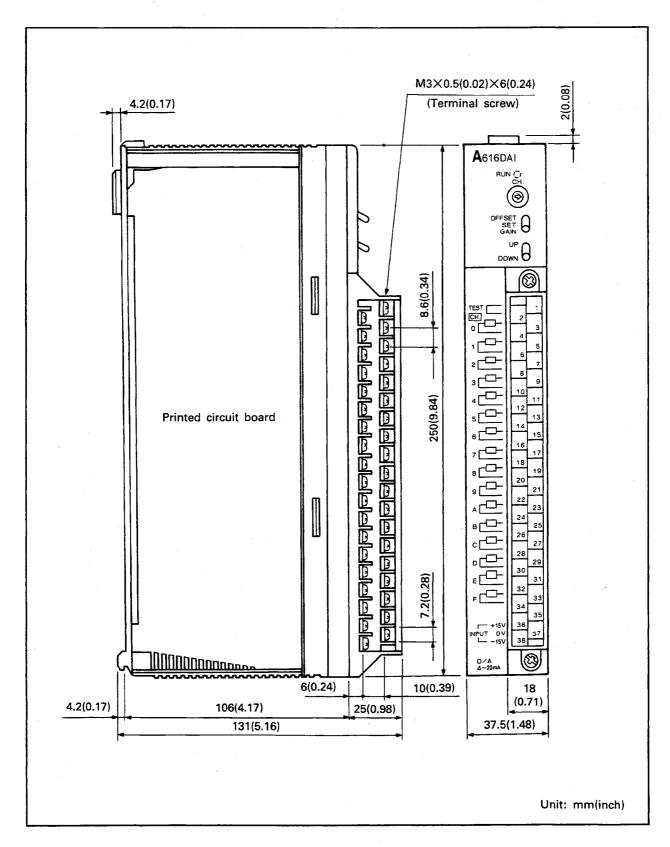

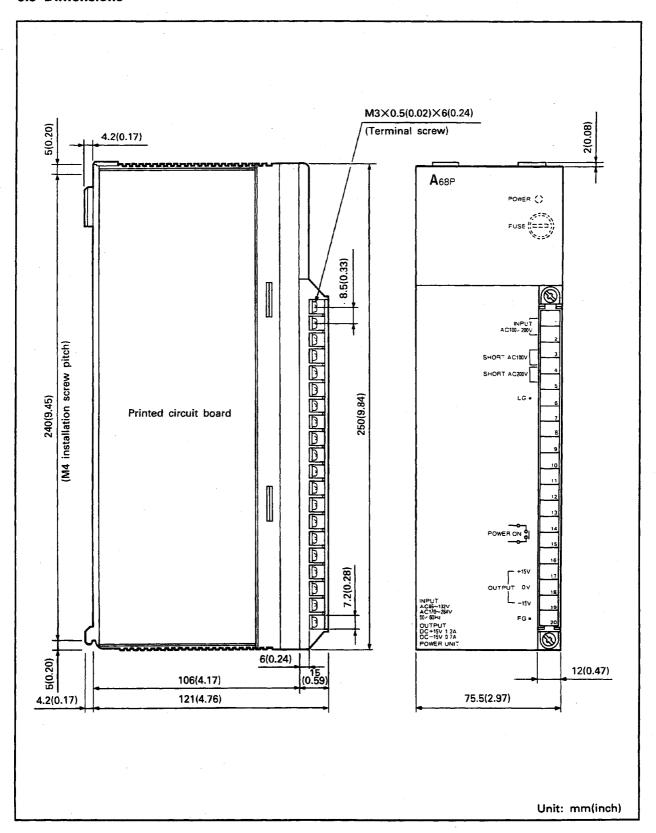

| ΔΡΡ             | ENDIX 1  | Dime      | nsions (A6                      | 16DAI) ·····                                                           | APP-1            |

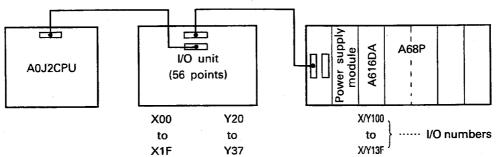

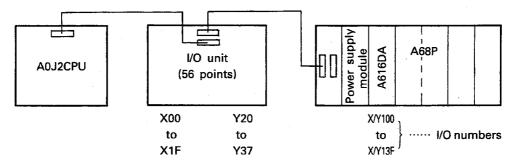

|                 | ENDIX 2  | Progr     | am Examr                        | oles for Compact Type CPU ······                                       | APP-2            |

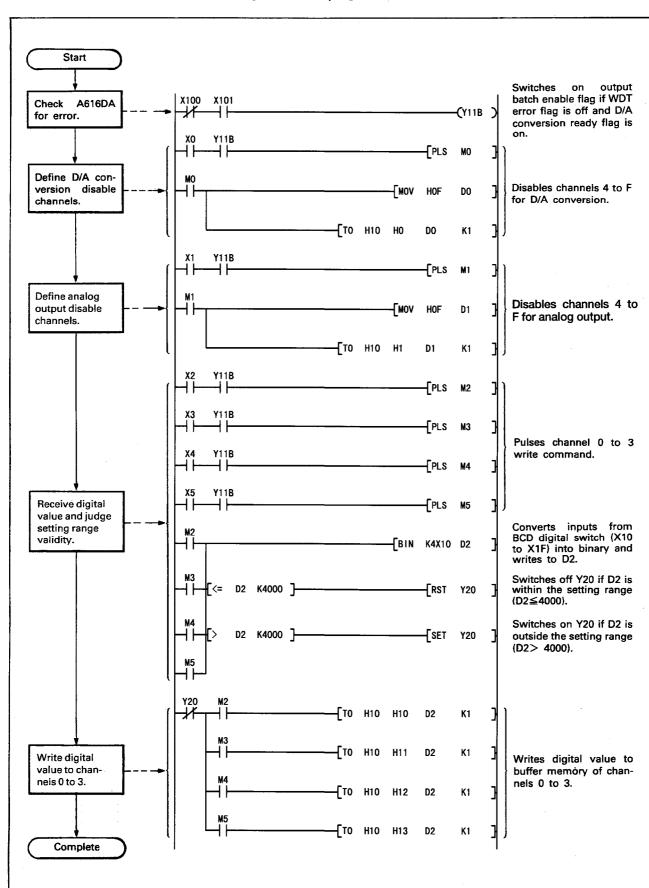

| <i>~</i>        | LINDIX   | 2.1       | Digital valu                    | ue setting program ······                                              | APP-2            |

|                 |          | 2.2       | Digital valu                    | ue setting error detection program·····                                | APP-4            |

| ΛPP             | ENDIX 3  | Δ68P      | Power Su                        | oply Module ·······                                                    | APP-6            |

| A1 F            |          | 3 1       | Specificati                     | ons                                                                    | APP-6            |

|                 |          | 3.2       | landling ··                     | ons                                                                    | APP-8            |

|                 |          |           | 3.2.1 Han                       | dling instructions ······                                              | APP-8            |

|                 |          |           | 3.2.2 Usii                      | ng instruction ······                                                  | APP-8            |

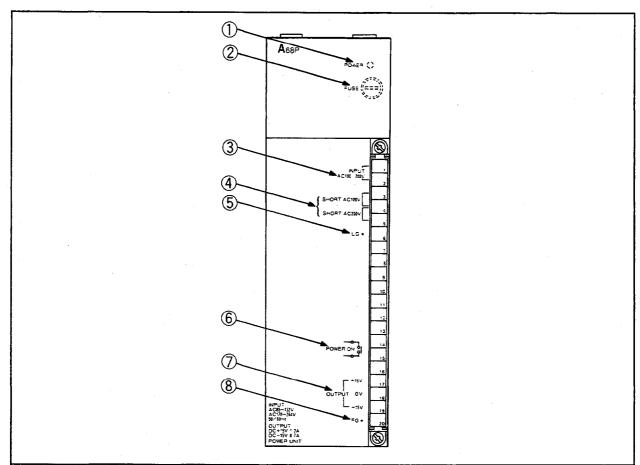

|                 |          |           | 3.2.2 Usii<br>3.2.3 Nor         | nenclature ······                                                      | APP-9            |

|                 |          | 3.3       | )imension                       | is ·····                                                               | APP-10           |

|                 |          | Ψ.υ       |                                 | <del></del>                                                            |                  |

### 1. INTRODUCTION

This manual gives specifications, handling, programming and other information on the A616DAI digital-to-analog converter module (referred to as "A616DA") for use with a MELSEC-A series CPU module.

The A616DA allows a 16-bit signed binary (data part: 12 bits) value defined from the ACPU to be converted into a 0 to 20mA current and to be output to 16 external devices.

### 1.1 Features

(1) Allows digital-to-analog conversion for 16 channels.

The A616DA can output analog values (current) to 16 external devices. (The channels are non-isolated.)

(2) Allows D/A conversion to be enabled/disabled per channel.

D/A conversion can be performed for only used channels by disabling unused channels for D/A conversion in the sequence program.

(3) Allows analog output to be enabled/disabled on a channel basis.

Analog value output can be enabled or disabled for each channel by the sequence program.

The channel disabled for analog output provides an analog output value of 0mA.

(4) Allows analog output to be held (for all channels) at STOP of ACPU.

A jumper allows analog output to be held or not held when the ACPU stops.

(5) Allows offset/gain adjustment to be made without potentiometers.

The offset and gain values can be specified by the UP/DOWN switch for each channel.

### 1.2 Generic Names of CPUs

The three generic CPU names used in this manual include the following CPU types:

### (1) Building block type CPU

A1CPU(P21/R21) **A2UCPU** A2CPU(P21/R21) A2UCPU-S1 A2CPU-S1(P21/R21) **A3UCPU** A3CPU(P21/R21) **A4UCPU** A1NCPU(P21/R21) A73CPU(P21/R21) A2NCPU(P21/R21) A3MCPU(P21/R21) A2NCPU-S1(P21/R21) A81CPU A3NCPU(P21/R21) **Q2ACPU** A3HCPU(P21/R21) Q2ACPU-S1 A2ACPU(P21/R21) **Q3ACPU** A2ACPU-S1(P21/R21) Q4ACPU A3ACPU(P21/R21) **Q4ARCPU**

### (2) Small-type building block type CPU

A1SCPU(S1)

A1SJCPU(S3)

A2SHCPU(S1)

A2ASCPU(S1/S30)

A1SJHCPU(S8)

A1SCPUC24-R2

A1SHCPU

A1SHCPU

(3) Compact type CPU A0J2CPU(P23/R23) A0J2HCPU(P23/R23) A52GCPU(T21B)

### 2. SYSTEM CONFIGURATION

### 2.1 Overall Configuration

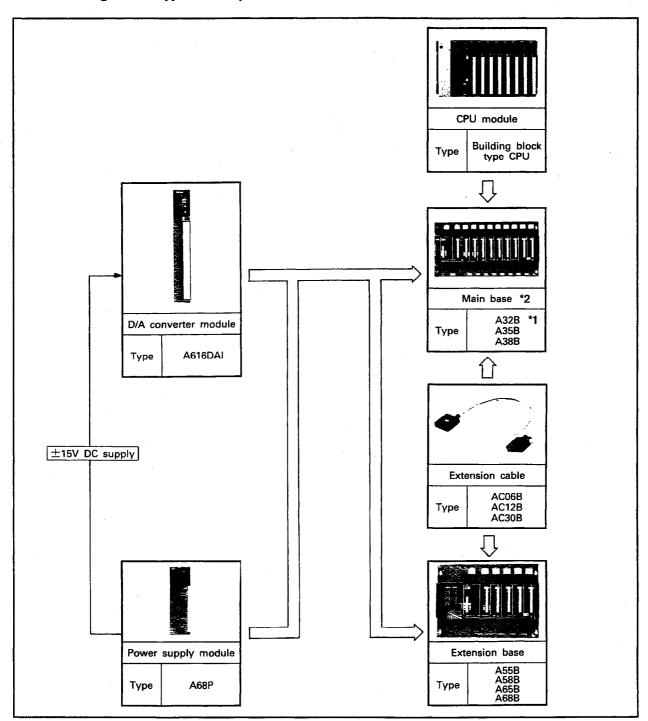

### 2.1.1 Building block type CPU system

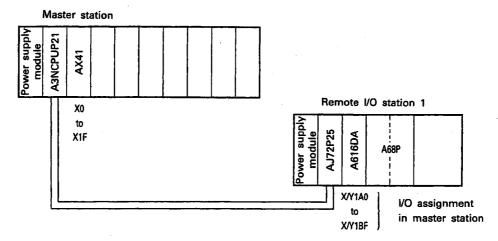

Fig. 2.1 Building Block Type CPU System Configuration

### **REMARKS**

- 1) \*1····· An extension base cannot be connected to the A32B.

- 2) \*2..... When using the A73CPU, A81CPU, the basic base will be the following.

- · A73CPU: A74B (A616DAV cannot be used with A74B)

- · A81CPU: A78B (Expansion base cannot be connected.)

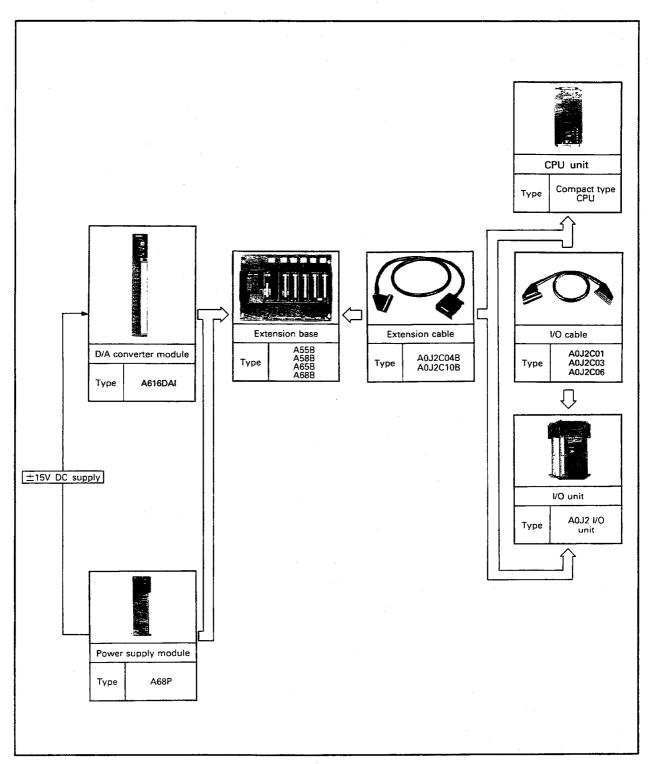

### 2.1.2 Compact type CPU system

Fig. 2.2 Compact Type CPU System Configuration

### 2.2 Applicable A-Series Systems

(1) The A616DA can be used with the following CPU modules:

| A0J2CPU   | A3UCPU      | A1SJHCPU(S8)    |

|-----------|-------------|-----------------|

| A0J2HCPU  | A4UCPU      | A1SCPU(S1)      |

| A1NCPU    | A73CPU      | A1SCPU24-R2     |

| A2NCPU    | A81CPU      | A1SHCPU         |

| A2NCPU-S1 | A1CPU       | A2SCPU(S1)      |

| A3NCPU    | A2CPU       | A2SHCPU(S1)     |

| A3HCPU    | A2CPU-S1    | A2ASCPU(S1/S30) |

| A3MCPU    | A3CPU       | A2USHCPU-S1     |

| A2ACPU    | Q2ACPU      | Q2ASCPU(S1)     |

| A2ACPU-S1 | Q2ACPU-S1   | Q2ASHCPU(S1)    |

| A3ACPU    | Q3ACPU      | A52GCPU         |

| A2UCPU    | Q4ACPU      | Q4ARCPU         |

| A2UCPU-S1 | A1SJCPU(S3) |                 |

- (2) The number of A616DAs used is unlimited if within the range of the I/O points of the CPU module used.

- (3) The A616DA may be loaded into any slot on the base unit with the following precautions:

- (a) When using the A616DA with the A55B or A58B extension bases (i.e. those without power supplies), select the power supply for the main base unit in accordance with the relevant CPU module User's Manual.

- (b) When used with the A3CPU(P21/R21), the A616DA cannot be loaded in the last slot of the 7th extension stage in a system for which I/O allocation has been made or link X, Y defined in the parameters.

- (These restrictions do not apply to A3NCPU, A3HCPU, A3MCPU, A73CPU, A3ACPU.)

- (4) In a data link system, the A616DA may be loaded into any of the master, local and remote I/O stations.

- Refer to the MELSECNET, MELSECNET/B data link system reference manual for examples of programs for remote I/O stations.

### POINT

(1) The A616DA cannot be used in an A0J2P25/R25 (remote I/O station).

### 2.3 Notes on Configuring the System

- (1) When using the A6161DA, an external power supply is required to supply  $\pm 15V$  DC to the A616DA.

- (a) The MELSEC-A series A68P power supply module for use on a base unit is available as a  $\pm 15$ V DC power supply. (For full information, see Appendix 3.)

- (b) If the A68P power supply module is not used, the power supply used must conform to the specifications given in Section 3.7. In this case, it is recommended to use noise filters with the A616DA. (See Section 4.6.3.)

- (c) With DC  $\pm 15$ V, make so that this is a system that will simultaneously be turned on and off with the A616DA system.

### 3. SPECIFICATIONS

Gives general specifications, A616DA performance specifications, I/O conversion characteristics, etc.

### 3.1 General Specifications

Table 3.1 shows the common specifications of various units used.

| item                          | Specifications                              |                                  |                    |                     |                         |                             |  |  |

|-------------------------------|---------------------------------------------|----------------------------------|--------------------|---------------------|-------------------------|-----------------------------|--|--|

| Operating ambient temperature | 0 to 55℃                                    |                                  |                    |                     |                         |                             |  |  |

| Storage ambient temperature   | -20 to 75℃                                  | -20 to 75℃                       |                    |                     |                         |                             |  |  |

| Operating ambient humidity    | 10 to 90%RH,                                | non-condensi                     | ng                 |                     |                         |                             |  |  |

| Storage ambient humidity      | 10 to 90%RH,                                | non-condensi                     | ng                 |                     |                         |                             |  |  |

|                               |                                             |                                  | Frequency          | Acceleration        | Amplitude               | Sweep count                 |  |  |

|                               | Conforming<br>to JIS B 3502,<br>IEC 61131-2 |                                  | Under intermittent | 10 to 57 Hz         |                         | 0.075 mm<br>(0.003 in.)     |  |  |

| Vibration resistance          |                                             | vibration                        | 57 to 150 Hz       | 9.8m/s²             |                         | 10 times each in X, Y, Z    |  |  |

|                               |                                             | Under<br>continuous<br>vibration | 10 to 57 Hz        |                     | 0.035 mm<br>(0.001 in.) | directions<br>(for 80 min.) |  |  |

|                               |                                             |                                  | 57 to 150 Hz       | 4.9m/s²             |                         |                             |  |  |

| Shock resistance              | Conforming to J                             | IIS B 3502, IEC                  | 61131-2 (147m/     | s², 3 times each ir | n X, Y, Z directio      | ns)                         |  |  |

| Operating ambiance            | No corrosive ga                             | s                                |                    |                     | -                       |                             |  |  |

| Operating height *3           | <b>2000 m</b> (6562 ft.                     | ) max.                           |                    |                     |                         |                             |  |  |

| Installation location         | Inside the contro                           | Inside <b>the control</b> panel  |                    |                     |                         |                             |  |  |

| Overvoltage categry *1        | II or less                                  |                                  |                    |                     |                         |                             |  |  |

| Pollution rate *2             | 2 or less                                   |                                  |                    |                     |                         |                             |  |  |

**Table 3-1 General Specifications**

- \*1: Indicates the distribution area where the device is assumed to be connected, from the public power distribution network to the local machine device.

- Category II is applied to the devices to which the power is supplied from a fixed equipment.

The surge resistace voltage of a rated 300 V device is 2500 V.

- \*2: This is an index which Indicates the occurrence rate of the conductive object in the anvironment where the device is used.

- Pollution rate II indicates that only non-conductive pollution may occur with a possibility of generating temporary conductivity due to accidental condensation.

- \*3: Do not use or store the PLC under pressure higher than the atmospheric pressure of altitude 0m. Doing so can cause a malfunction.

- When using the PLC under pressure, please contact your sales representative.

### 3.2 Performance Specifications

| lte                                         | m                                      | Specifications                                                                                                 |         |  |  |  |  |

|---------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| Digital<br>(ACPU to                         |                                        | 1) 16-bit signed binary (data part: 12 bits) 2) Setting range: 0 to 4095                                       |         |  |  |  |  |

| Analog ou<br>(A616DA to ex                  |                                        | 0 to 20 DC (External load resistance: 0 to 600Ω)                                                               |         |  |  |  |  |

|                                             |                                        | Digital input Analog output                                                                                    |         |  |  |  |  |

| I/O chara                                   | ctorictics                             | +4000 +20mA                                                                                                    | Section |  |  |  |  |

| VO Cilara                                   | Cleristics                             | +2000 +12mA                                                                                                    | 3.4     |  |  |  |  |

|                                             |                                        | 0 4mA                                                                                                          |         |  |  |  |  |

| Digital value                               |                                        | 1/4000                                                                                                         |         |  |  |  |  |

| Overall acc<br>(accuracy against the        | curacy (%)<br>ne maximum value)        | $\pm 0.6$ ( $\pm 120\mu$ A ) ( $\pm 0.3$ ( $\pm 60\mu$ A) when the ambient temperature is 25°C)                |         |  |  |  |  |

| Sampling period (ms)                        |                                        | 1.5 + 0.5 × (number of D/A conversion enable channels)                                                         |         |  |  |  |  |

| Conversion time (ms)                        |                                        | 0.5 (time required for conversion from 0 to 20/20mA to 0mA)                                                    |         |  |  |  |  |

| Absolute maximum output (V)                 |                                        | 15                                                                                                             |         |  |  |  |  |

| Number of analog                            | output channels                        | 16 channels/module                                                                                             |         |  |  |  |  |

| Isolation                                   |                                        | Photocoupler isolated between output terminals and PLC power supply.     Non-isolated between A616DA channels. |         |  |  |  |  |

| Number of                                   | I/O points                             | 32                                                                                                             |         |  |  |  |  |

| Term                                        | inals                                  | 38-point terminal block                                                                                        |         |  |  |  |  |

| Wire size                                   | e (mm²)                                | 0.75 to 2 (18 to 14 AWG)                                                                                       |         |  |  |  |  |

| Solderless                                  | terminal                               | V1.25-3, V1.25-YS3A, V2-S3, V2-YS3A                                                                            |         |  |  |  |  |

| Internal current consumption<br>(5V DC) (A) |                                        | 0.3                                                                                                            |         |  |  |  |  |

| External supply                             | cternal supply Voltage +15V DC/-15V DC |                                                                                                                | Section |  |  |  |  |

| power*                                      | Current                                | 0.53A for +15V DC/0.125A for -15V DC                                                                           | 3.7     |  |  |  |  |

| External dimens                             | sions mm(inch)                         | 250(9.84) × 37.5(1.48) × 131(5.16)                                                                             |         |  |  |  |  |

| Weig                                        | ht kg                                  | 0.69                                                                                                           |         |  |  |  |  |

Table 3.2 Performance Specifications

### **REMARKS**

### 1) Overall accuracy

Accuracy in reference to maximum value (20mA).

Due to the operating environment (ambient temperature, noise), there will be fluctuation within a range of 20mA ( $\pm 0.6\%(\pm 120\,\mu$  A))

A)) When the ambient temperature is 25°C, there will be fluctuation within a range of 20mA  $\pm 0.3\%$  ( $\pm 60~\mu$  A)

2) \* ······ One A68P power supply module can supply  $\pm$ 15V DC to two A616DAs. (See Appendix 3 for full information on the A68P power supply module.)

### 3.3 Analog Output Control Functions

(1) Table 3.3 gives various facilities for controlling analog output.

| Item                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Setting<br>Method |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Analog output<br>HOLD/CLEAR<br>setting<br>(for all<br>16 channels)      | <ul> <li>(1) Using the jumper, specify whether the analog output at the time of STOP is held (HOLD) or cleared (CLEAR) when the ACPU is set to STOP by the RUN key switch, etc.</li> <li>(a) CLEAR setting:     STOP OmA or offset value is output.     RUN Digital value specified from the ACPU is converted into an analog value and is output only while the output batch enable flag (Y1B) is on.</li> <li>(b) HOLD setting:     STOP Analog value at the time of STOP is retained.     RUN Digital value specified from the ACPU is converted into an analog value and is output independently of the ON/OFF state of the output batch enable flag (Y1B).</li> <li>(2) When the ACPU stops operation on detection of an error, the analog output value is set to OmA independently of the analog output HOLD/ CLEAR setting.</li> </ul> | Section 4.4.1     |

| D/A conversion<br>disable channel<br>setting<br>(on a channel<br>basis) | <ul> <li>(1) Using the sequence program, specify the channel to be disabled for D/A conversion in order to reduce the sampling period.</li> <li>(All 16 channels are enabled for D/A conversion when the ACPU is powered up or reset.)</li> <li>(a) D/A conversion enable channel  ——————————————————————————————————</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Section 5.3.2     |

| Analog output<br>disable channel<br>setting<br>(on a channel<br>basis)  | <ul> <li>(1) Using the sequence program, specify the channel to be disabled for analog value output.</li> <li>(All 16 channels are enabled for analog output when the ACPU is powered up or reset.)</li> <li>(a) Analog output enable channel  ————Outputs the offset value or an analog value converted.</li> <li>(b) Analog output disable channel  ————Outputs 0mA.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Section 5.3.3     |

### **Table 3.3 Analog Output Control Functions**

(2) As indicated in Table 3.4, analog output values depend on the settings of the analog output control functions indicated in Table 3.3.

| Setting combination | Analog Output<br>HOLD/CLEAR<br>Setting            | CLEAR                       |              |                |                |                | HOLD                                                |              |                |

|---------------------|---------------------------------------------------|-----------------------------|--------------|----------------|----------------|----------------|-----------------------------------------------------|--------------|----------------|

|                     | Output batch enable flag (Y1B)                    | ON                          |              |                | OFF            |                | ON/OFF                                              |              |                |

|                     | Analog Output<br>disable channel<br>setting       | Enable                      |              | Disable        | Enable         | Disable        | Enable                                              |              | Disable        |

| Execution on status | D/A conversion<br>disable channel<br>setting      | Enable                      | Disable      | Enable/Disable | Enable/Disable | Enable/Disable | Enable                                              | Disable      | Enable/Disable |

| When                | PLC CPU RUN                                       | D/A conversion value output | Offset value | 0V             | Offset value   | 0V             | D/A conversion value output                         | Offset value | OV             |

| When                | PLC CPU STOP                                      | ov                          | Offset value | ov             | Offset value   | 0V             | Outputs the analog output value preceeding the stop |              | ov             |

| When PL             | C CPU error occurs                                |                             |              |                | 0              | V              |                                                     |              |                |

|                     | /O station link error ted to remote I/O station). |                             |              |                | 0              | V              |                                                     |              |                |

**Table 3.4 Analog Output Values**

### 3.4 I/O Conversion Characteristics

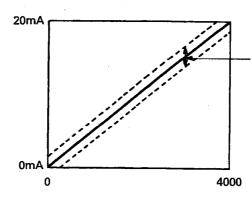

### 3.4.1 I/O conversion characteristics

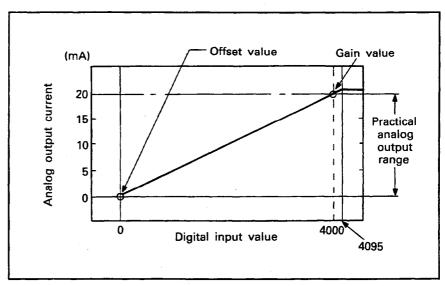

(1) I/O conversion characteristics

I/O conversion characteristics are provided to convert a digital value specified from the ACPU into an analog value and are indicated by an inclination connected between an offset value and a gain value.

- (2) Offset value and gain value

- (a) The offset and gain values are defined as follows:

- Offset value ···· Current output from the A616DA when the digital value specified from the ACPU is 0.

- 2) Gain value ······ Current output from the A616DA when the digital value specified from the ACPU is 4000.

- (b) The factory-set offset and gain values are as follows:

- 1) Offset value ··· 0mA

- 2) Gain value ····· 20mA

- (c) The offset and gain values may be changed in test mode for each channel.

- (3) I/O conversion characteristic example

Fig. 3.1 I/O Conversion Characteristic Example

(4) Relation between offset/gain value and analog output

The resolution of the A616DA can be changed as appropriate by the offset/gain value setting.

The analog value resolution and analog output value are calculated by the following equations:

$$(\text{Resolution}) = \frac{(\text{gain value}) - (\text{offset value})}{4000}$$

$$(\text{Analog output}) = \frac{(\text{gain value}) - (\text{offset value})}{4000}$$

$$\times (\text{digital input value}) + (\text{offset value})$$

$$= (\text{resolution}) \times (\text{digital input value})$$

$$+ (\text{offset value})$$

As the maximum analog value resolution of the A616DA is  $2.64\,\mu$  A, the variation of the analog output value for a change of 1 in the digital input value may not be as calculated above.

### 3.4.2 I/O conversion characteristics in response to offset/gain value changes

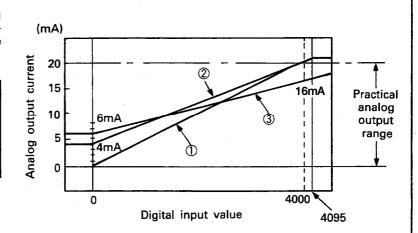

(1) Offset/gain values vs. I/O conversion characteristics

The relation between the following offset/gain settings and I/O conversion characteristics is shown on the right.

| No. | Offset Value | Gain Value |

|-----|--------------|------------|

| 1   | 0mA          | 20mA       |

| 2   | 4mA          | 20mA       |

| 3   | 6mA          | 16mA       |

r - Example - - - -

The analog output voltages are as follows at the digital input value settings of 2000 and 1000 for the characteristic graphs ① to ③.

| No.     | Digital Input Value | Analog Output Value |

|---------|---------------------|---------------------|

| ①       | 2000                | 10mA                |

|         | 1000                | 5mA                 |

| <u></u> | 2000                | 12mA                |

| 2       | 1000                | 8mA                 |

|         | 2000                | 11mA                |

| 3       | 1000                | 8.5mA               |

Fig. 3.2 Offset/Gain Values vs. I/O Conversion Characteristics

3

### 3.5 D/A Conversion Processing Time

The processing time required for digital-to-analog conversion and output to the external equipment is calculated as follows:

(Processing time) = (sampling period) + (conversion time)

(a) Sampling period

······ Cycle of D/A conversion processing for the same channel.

(b) Conversion speed

...... Time required for the analog value to change to the set value.

### 3.5.1 Sampling period

(1) The A616DA performs D/A conversion for a D/A conversion enable channel which is switched to another per 0.5ms. A cycle of executing D/A conversion for the same channel is referred to as a sampling period, which is calculated as follows:

(Sampling period) =

$$\underline{1.5} + 0.5 \times \text{(number of D/A conversion)} \text{(ms)}$$

Constant

(2) The sampling period can be reduced by defining unused channels as channels disabled for D/A conversion.

- Example -----

(1) The sampling period is as follows if channels 0 to F (16 channels) are enabled for D/A conversion.

Sampling period =  $1.5 + 0.5 \times 16 = 9.5$  (ms)

(2) The sampling period is as follows if channels 4 to 7 and C to F (8 channels) are disabled for D/A conversion.

Sampling period =  $1.5 + 0.5 \times 8 = 5.5$  (ms)

### 3.5.2 Conversion speed

- Indicates the processing time required for the analog value to change to the specified value after D/A conversion processing.

- (2) The maximum conversion speed (0 to 20mA or 20 to 0mA) is 0.5ms.

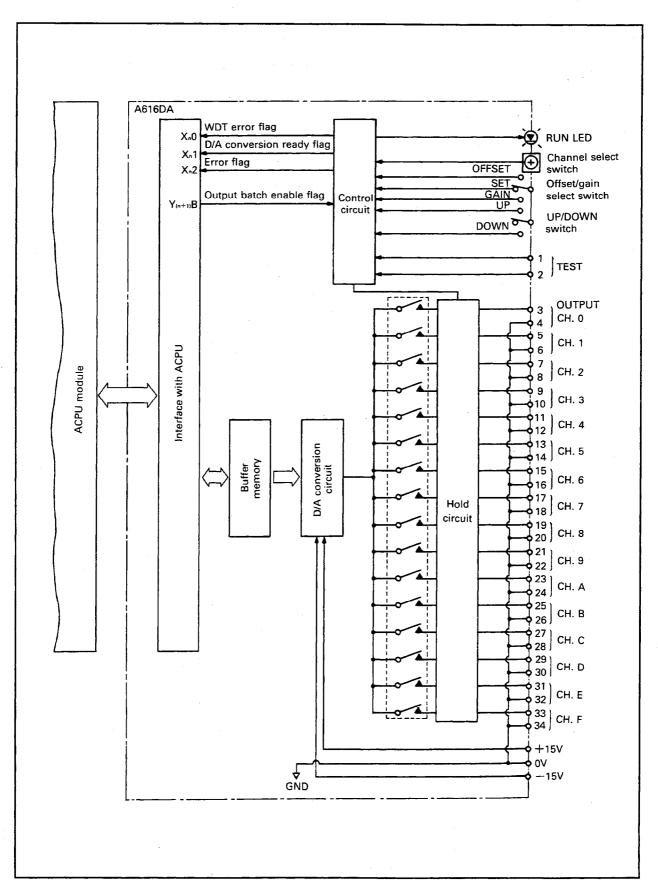

### 3.6 Function Block Diagram

Fig. 3.3 A616DA Function Block Diagram

### 3.7 External Supply Power (±15V DC) Specifications

The A68P power supply module is recommended for use as a power supply for providing  $\pm 15V$  DC to the A616DA. (Full information on the A68P power supply module is given in Appendix 3.)

When the A68P power supply module is not used, the power supply used to supply  $\pm 15V$  DC to the A616DA must conform to the specifications given in Table 3.5.

| Item                       |         | Specifications                   |

|----------------------------|---------|----------------------------------|

| Voltage                    |         | +15V DC ±3% (14.55V to 15.45V)   |

|                            |         | -15V DC ±3% (-14.55V to -15.45V) |

| Current*                   | +15V DC | 0.53A                            |

|                            | -15V DC | 0.125A                           |

| Ripple voltage             |         | 50mVpp max.                      |

| Spike voltag               |         | 100mVpp max.                     |

| Transient output variation |         | Within ±1V                       |

Table 3.5 External Supply Power ( $\pm 15 \text{V}$  DC) Specifications

### REMARKS

1) \* ····· The currents indicated in Table 3.5 are those for one A616DA.

### 4. PRE-OPERATION SETTINGS AND PROCEDURES

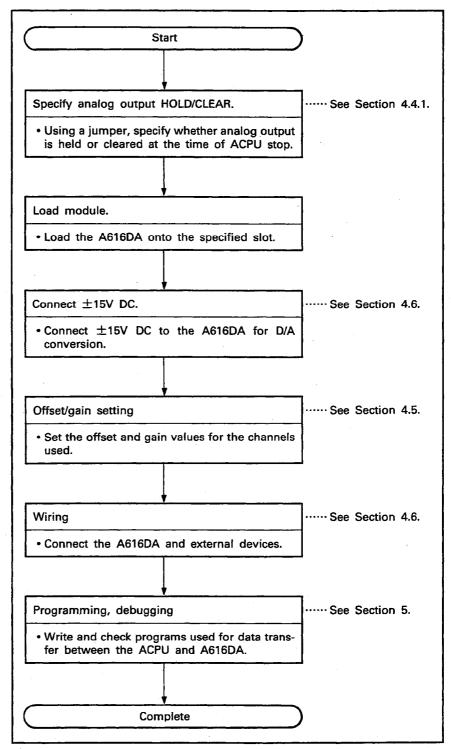

### 4.1 Pre-Operation Procedure

Fig. 4.1 Pre-Operation Procedure

# 4. PRE-OPERATION SETTING AND PROCEDURES

### 4.2 Handling Instructions

- (1) Protect the A616DA and its terminal block from impact loads.

- (2) Do not remove the printed circuit boards from the housing. There are no user-serviceable parts on the boards.

- (3) Ensure that no conductive debris can enter the module. If it does, make sure that it is removed. Guard particularly against wire offcuts.

- (4) Tighten the screws as specified below:

| Screw                                            | Tightening Torque Range |

|--------------------------------------------------|-------------------------|

| I/O terminal screw (M3 screw)                    | 39 to 58 N∙cm           |

| I/O terminal block installation screw (M4 screw) | 78 to 118 N·cm          |

(5) To load the module onto the base, press the module against the base so that the catch on the top of the unit is securely locked. To unload the module, push the catch, and after the catch is disengaged from the base, pull the module toward you.

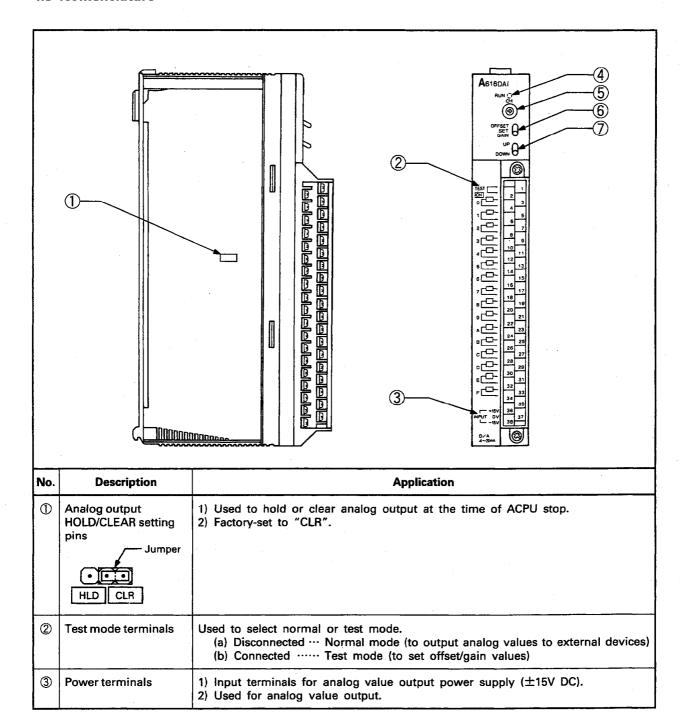

### 4.3 Nomenclature

4

# 4. PRE-OPERATION SETTING AND PROCEDURES

| No. | Description               | Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | "RUN" LED                 | 1) Indicates the operating status of the A616DA. 2) Normal mode (a) On Indicates that the A616DA is operating without fault. (b) Off • 5V DC is not supplied to the A616DA. • A616DA is in WDT error. • A616DA hardware fault has occurred. • ACPU has detected an error and stopped operation. (c) Fast flicker • Offset/gain value setting is not normal. (at intervals of 0.1sec) • A616DA hardware fault. 3) Test mode (a) Flicker • OFFSET/GAIN select switch is in "OFFSET" or "GAIN" position.  At intervals of 0.1sec • OFFSET/GAIN select switch is in "OFFSET" or "GAIN" position. • The high or low limit of the allowed range has been exceeded during offset/gain value setting using the UP/DOWN switch. • Offset value setting is greater than gain value setting using the UP/DOWN switch. (b) Off OFFSET/GAIN select switch is in "SET" position. |

| \$  | Channel select switch     | 1) Used to specify the channel (CH.0 to F) for offset/gain adjustment. 2) Channel should be switched when the OFFSET/GAIN select switch is in "SET" position. 3) Only valid in test mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | OFFSET/GAIN select switch | Used to select any of the following modes:  (a) OFFSET position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7   | UP/DOWN switch            | <ol> <li>Used to define the offset/gain value for the specified channel.</li> <li>Increases or decreases the offset or gain value at the following rate:         <ul> <li>(a) UP/DOWN position for less than 1.5 seconds: Increase or decrease of 2.64 μ A at one time.</li> <li>(b) UP/DOWN position for 1.5 seconds or more: Increase or decrease of 2.64 μ A per 0.05sec.</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### 4.4 Settings

The following settings should have been performed before loading the A616DA to the base unit.

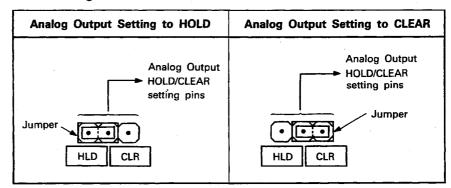

### 4.4.1 Setting analog output to HOLD/CLEAR

Set analog output at ACPU STOP to HOLD or CLEAR by inserting the jumper into the pins on the left-hand side of the A616DA.

- (a) Setting analog output to HOLD: Set the HOLD/CLEAR setting jumper to the "HLD" position. (See Fig. 4.2.)

- (b) Setting analog output to CLEAR: Set the HOLD/CLEAR setting jumper to the "CLR" position. (See Fig. 4.2.)

Fig. 4.2 Analog Output HOLD/CLEAR Setting for ACPU Stop

### 4.5 Offset/Gain Setting

(1) The offset and gain values are factory-set to output the currents indicated in Table 4.1.

|                   | Output Current |

|-------------------|----------------|

| Gain value (mA)   | 20             |

| Offset value (mA) | 4              |

Table 4.1 Factory-Set Offset/Gain Values

(2) The offset and gain values may be changed and fine-adjusted by offset/gain setting in test mode.

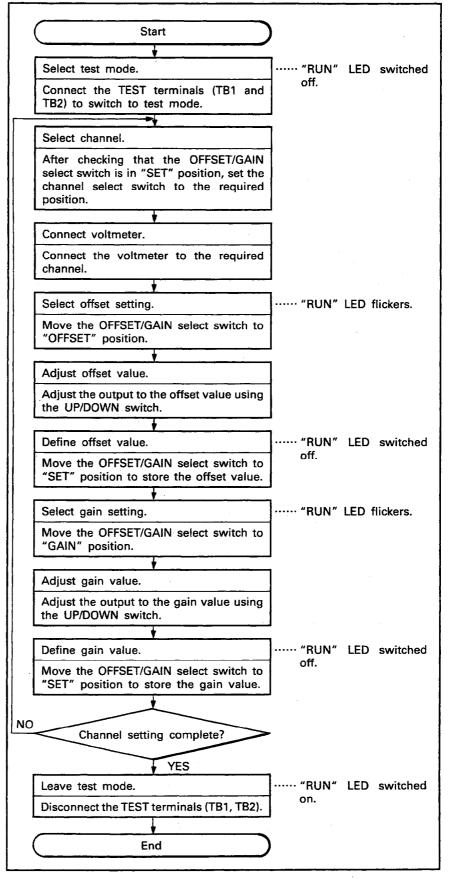

### 4.5.1 Notes on offset/gain setting

- (1) Do not select test mode during execution of D/A conversion. Selecting test mode stops D/A conversion of all channels and affects control of external devices. Returning from test mode to normal mode resumes D/A conversion with new offset/gain values.

- (2) Offset/gain setting is allowed between 0mA and 20mA. If any value set is outside the above range, overall accuracy may not be within the range of performance specifications (see Section 3.2.).

- (3) The defined value is stored when the OFFSET/GAIN select switch is set to the "SET" position.

The offset and gain value remain unchanged if test mode is terminated with the OFFSET/GAIN select switch in the "OFFSET" or "GAIN" position.

- (4) Before switching from one channel to another in test mode, the OFFSET/GAIN select switch should be set to the "SET" position.

If the channel is switched with the OFFSET/GAIN select switch in the "OFFSET" or "GAIN" position, the offset/gain value of the previous channel remains unchanged and the set value is stored to the new channel when the switch is set to "SET".

### Example

- (1) The gain value of channel 3 has been changed from 20mA to 10mA and channel 4 has been selected with the OFFSET/GAIN select switch in the "GAIN" position.

- (a) Gain value of channel 3 ...... Remains 20mA.

- (b) Gain value of channel 4 ..... 10mA is output.

10mA is stored as a gain value when the OFFSET/GAIN select switch is set to "SET".

# 4. PRE-OPERATION SETTING AND PROCEDURES

(5) The "RUN" LED flickers fast at intervals of 0.1 seconds to indicate that the offset/gain value specified has exceeded the allowed range.

When the "RUN" LED is flickering fast, the offset/gain value remains unchanged if the OFFSET/GAIN select switch is set to "SET".

# 4. PRE-OPERATION SETTING AND PROCEDURES

### 4.5.2 Offset/gain setting procedure

Fig. 4.3 Offset/Gain Setting Procedure

### 4.6 Wiring

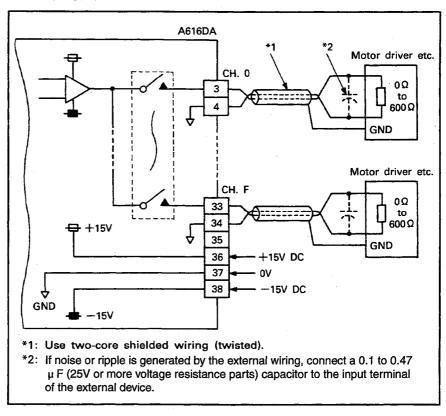

### 4.6.1 Wiring instructions

Protect external wiring against noise with the following precautions:

- (1) Separate AC and DC wiring.

- (2) Separate main circuit and/or high voltage wiring from control and signal wiring.

- (3) Where applicable, ground the shielding of all wires to a common ground point.

### 4.6.2 Connection of A616DA and external devices

Fig. 4.4 Connection Example of A616DA and External Devices

### 4.6.3 Connection of ±15V DC to the A616DA

$\pm$ 15V DC may be supplied to the A616DA in either of the following ways:

- (a) A68P power supply module

- (b) External power supply

Use of the A68P power supply module

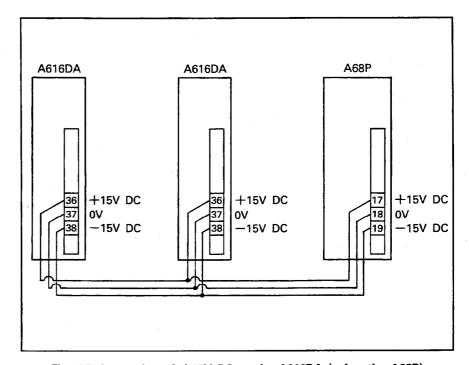

- (1) Connect the +15V, 0V and -15V terminals of the A616DA with those of the A68P.

- (2) One A68P can supply  $\pm 15V$  DC to four A616DAs.

Fig. 4.5 Connection of  $\pm 15 \text{V}$  DC to the A616DA (using the A68P)

(3) To protect the A616DA, ±15V DC must not be supplied to one A616DA from several A68Ps connected in parallel.

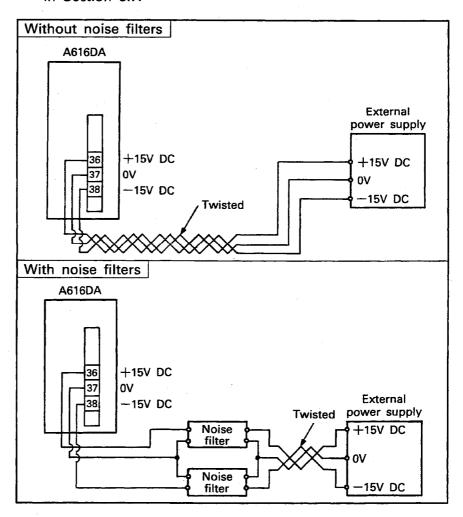

### Use of external power supply

- (1) Connect the  $\pm 15V$ , 0V and  $\pm 15V$  terminals of the A616DA with those of the external power supply.

- (2) When the external power supply is used, it is recommended to use noise filters with the A616DA:

- (3) The power specifications of the external power supply is given in Section 3.7.

# POINT

- (1) The cables between the noise filters and A616DA must not be bundled with any other cable.

- (2) The cables between the noise filters and A616DA must be as short as possible.

# **MEMO**

### 5. PROGRAMMING

This section explains the programming procedure for use of the A616DA.

When applying any of the program examples introduced in this chapter to the actual system, verify the applicability and confirm that no problems will occur in the system control.

## 5.1 Programming Procedure

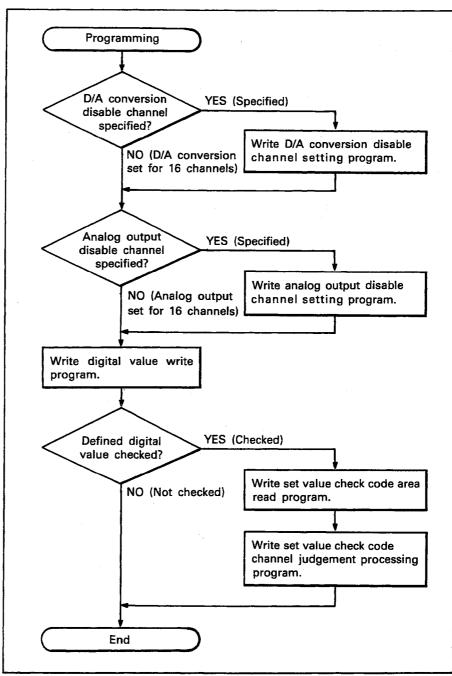

Program data transfer between the ACPU and A616DA as indicated in Fig. 5.1.

Fig. 5.1 Programming Procedure

5

### 5.2 I/O List for ACPU

# 5.2.1 Input list

- (1) Input signals given from the A616DA to the ACPU are  $X_n0$  to  $X_{(n+1)}F^*$  (32 points).

- (2) Input signal specifications

| Input<br>Signal                                    | Name                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| X <sub>n</sub> 0                                   | Watch dog timer error                          | Switched on if a watch dog timer error occurs in the A616DA.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                    |                                                | Normal mode (other than test mode)                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| <b>X</b> ₁1                                        | D/A conversion<br>ready flag                   | <ol> <li>(1) Switched on when D/A conversion is ready after the ACPU is powered up or reset.</li> <li>(2) Switched off if:         <ul> <li>(a) WDT error occurs in the A616DA</li> <li>(b) A616DA hardware fault occurs; or</li> <li>(c) ACPU has detected an error and stopped operation.</li> </ul> </li> <li>(3) Data transfer between ACPU and A616DA is made after X<sub>n</sub>1 is switched on. (X<sub>n</sub>1 is used as a read/write interlock.)</li> </ol> |  |  |  |

|                                                    |                                                | Test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                    |                                                | Switched off when normal mode is switched to test mode.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| X₁2                                                | Error flag                                     | <ul> <li>(1) Switched on if the digital input from the ACPU for any channel is outside the allowed range (0 to 4095).</li> <li>(2) Switched off when all values in the buffer memory error code area (30<sub>H</sub> to 3F<sub>H</sub>) are set to 0.</li> </ul>                                                                                                                                                                                                       |  |  |  |

| X <sub>2</sub> 3                                   |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| to<br>X <sub>(n+1)</sub> C                         |                                                | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

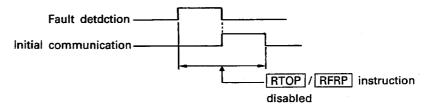

| X <sub>(n+1)</sub> D<br>to<br>X <sub>(n+1)</sub> F | RFRP, RTOP<br>instruction<br>interlock signals | Only used when the A616DA is loaded into a remote I/O station.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

Table 5.1 Input Signal Specifications

### **REMARKS**

1) \*  $\cdots$  n in X<sub>n</sub>0 to X<sub>n+1</sub>F indicates the head address of the slot being used for the A616DA.

## Example

$_{n}$  = 00 if the A616DA is used on slot 0 of the main base.  $X_{n}0 \rightarrow X_{000}$

### 5.2.2 Output list

- (1) Output signals given from the ACPU to the A616DA are  $Y_n0$  to  $Y_{(n+1)}F^*$  (32 points).

- (2) Output signal specifications

| Output<br>Signal                                   | Name                                           | Description                                                                                                                                                                                                                         |

|----------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y <sub>n</sub> 0<br>to<br>Y <sub>n</sub> C         |                                                | Reserved.                                                                                                                                                                                                                           |

| Y₁D<br>to<br>Y₁F                                   | RFRP, RTOP<br>instruction<br>interlock signals | Only used when the A616DA is loaded into a remote I/O station.                                                                                                                                                                      |

| Y <sub>(n+1)</sub> 0<br>to<br>Y <sub>(n+1)</sub> A |                                                | Reserved.                                                                                                                                                                                                                           |

| Y(n+1)B                                            | Output batch<br>enable flag                    | <ol> <li>Shared among channels 0 to F.</li> <li>For analog output in normal mode, see Table 3.4.</li> <li>In test mode, offset/gain values are output independently of the ON/OFF state of the output batch enable flag.</li> </ol> |

| Y <sub>(n+1)</sub> C<br>to<br>Y <sub>(n+1)</sub> F | -                                              | Reserved.                                                                                                                                                                                                                           |

**Table 5.2 Output Signal Specifications**

### **IMPORTANT**

$Y_n0$  to  $Y_nC$ ,  $Y_{(n+1)}$  to  $Y_{(n+1)}A$ , and  $Y_{(n+1)}C$  to  $Y_{(n+1)}F$  are reserved for the system and must not be used (switched on/off) in the sequence program.

### REMARKS

1) \* ····· n in Yn0 to Yn+1F indicates the head address of the slot being used for the A616DA.

### Example

$_{n}$  = 00 if the A616DA is used on slot 0 of the main base.  $Y_{n0} \rightarrow Y_{000}$

# 5.3 Buffer Memory

- (1) The A616DA has a buffer memory (not battery backed) for data communication with the ACPU.

- (2) The buffer memory assignment and data maps are indicated below.

### 5.3.1 Buffer memory assignment

| ddress                                  | Communicat | tion with ACPU                        | Relevant Section |  |

|-----------------------------------------|------------|---------------------------------------|------------------|--|

| łexadecimal)                            | Read       | Write                                 |                  |  |

| O D/A conversion enable/disable channel | 0          | 0                                     | Section 5.3.2    |  |

| 1 Analog output enable/disable channel  | 0          | 0                                     | Section 5.3.3    |  |

| 2 to Reserved                           | ~<br>~ -   | _                                     | _                |  |

| F CH. 0 digital value                   |            |                                       |                  |  |

| 11 CH. 1 digital value                  |            |                                       |                  |  |

| 12 CH. 2 digital value                  |            |                                       | ·                |  |

| 13 CH. 3 digital value                  |            | · ·                                   |                  |  |

| 14 CH. 4 digital value                  |            |                                       |                  |  |

| 15 CH. 5 digital value                  |            |                                       |                  |  |

| 16 CH. 6 digital value                  | 1          |                                       |                  |  |

| 17 CH. 7 digital value                  |            |                                       |                  |  |

| 18 CH. 8 digital value                  |            |                                       | Section 5.3.4    |  |

| 19 CH. 9 digital value                  |            |                                       |                  |  |

| 1A CH. A digital value                  |            |                                       |                  |  |

| 1B CH. B digital value                  |            |                                       |                  |  |

| 1C CH. C digital value                  |            |                                       |                  |  |

| 1D CH. D digital value                  |            |                                       |                  |  |

| 1E CH. E digital value                  | , i        | •                                     |                  |  |

| 1F CH. F digital value                  |            |                                       |                  |  |

| 20                                      |            |                                       |                  |  |

| to Reserved                             | <b>∻</b> – | _                                     | · <del>-</del>   |  |

| 2F                                      |            |                                       |                  |  |

| 30 CH. 0 set value check code           |            |                                       |                  |  |

| 31 CH. 1 set value check code           |            | ·                                     |                  |  |

| 32 CH. 2 set value check code           |            |                                       |                  |  |

| 33 CH. 3 set value check code           |            |                                       |                  |  |

| 34 CH. 4 set value check code           |            |                                       |                  |  |

| 35 CH. 5 set value check code           |            |                                       |                  |  |

| 36 CH. 6 set value check code           | •          |                                       |                  |  |

| 37 CH. 7 set value check code           |            |                                       | Section 5.3.5    |  |

| 38 CH. 8 set value check code           |            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 000              |  |

| 39 CH. 9 set value check code           |            |                                       |                  |  |

| 3A CH. A set value check code           |            | 1                                     |                  |  |

| 3B CH. B set value check code           |            |                                       |                  |  |

| 3C CH. C set value check code           |            |                                       |                  |  |

| 3D CH. D set value check code           |            |                                       |                  |  |

| 3E CH. E set value check code           |            |                                       |                  |  |

| 3F CH. F set value check code           |            |                                       | <u> </u>         |  |

Fig. 5.2 Buffer Memory Assignment

# 5.3.2 D/A conversion enable/disable channel area (Address 0<sub>H</sub>)

- (1) Defines whether D/A conversion is performed or not on a channel-by-channel basis.

- (2) All channels are enabled for D/A conversion when:

- (a) Power is switched on; or

- (b) ACPU is reset.

- (3) D/A conversion enable/disable is defined by 1/0.

- (a) Enable .....1

- (b) Disable .....0

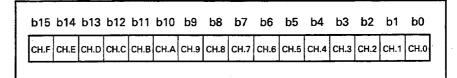

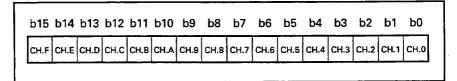

- (4) The D/A conversion enable/disable channel area data map is shown below:

Fig. 5.3 D/A Conversion Enable/Disable Channel Area Data Map

### 5.3.3 Analog output enable/disable channel area (Address 1+)

- (1) Defines output enable/disable for the converted analog value per channel.

- (2) All channels are enabled for output when:

- (a) Power is switched on; or

- (b) ACPU is reset.

- (3) Output enable/disable is defined by 1/0.

- (a) Enable .....1

- (b) Disable .... 0

- (4) The analog output enable/disable channel area data map is shown below:

Fig. 5.4 Analog Output Enable/Disable Channel Area Data Map

### 5.3.4 CH.0 to CH.F digital value area (Addresses 10, to 1F,)

- (1) Write digital values to this area from the ACPU for D/A conversion.

- (2) Digital values of all channels are set to 0 if:

- (a) D/A conversion ready (X01) is on after power on; or

- (b) D/A conversion ready (X01) is switched on after the ACPU is reset.

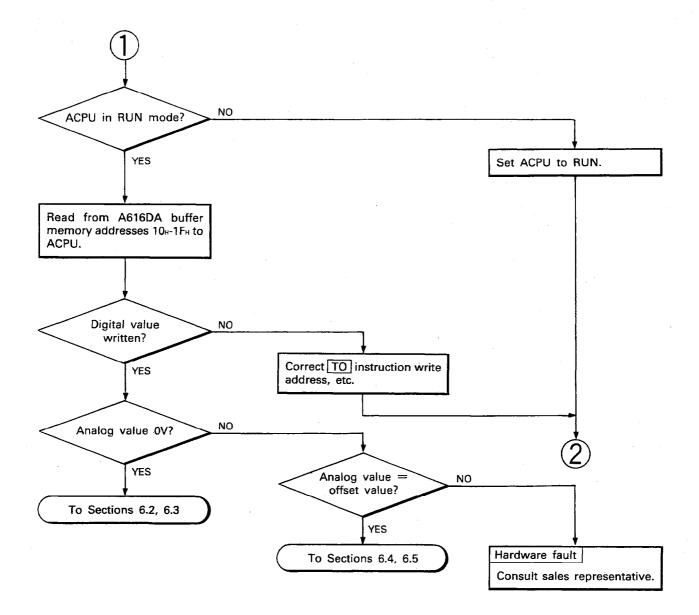

- (3) Any digital value specified should be a 16-bit signed binary between 0 and +4095. Any digital value outside this range is changed to a value indicated below before D/A conversion, and the corresponding check code is written to the set value check code area (addresses 30<sub>H</sub> to 3F<sub>H</sub>).